System on chip что это

Система на кристалле

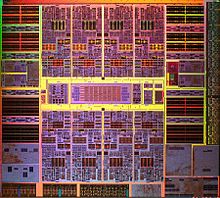

Система на кристалле (однокристальная система) — в микроэлектронике — электронная схема, выполняющая функции целого устройства (например, компьютера) и размещенная на одной интегральной схеме.

В англоязычной литературе называется System-on-a-Chip, SoC .

В зависимости от назначения она может оперировать как цифровыми сигналами, так и аналоговыми, аналого-цифровыми, а также частотами радиодиапазона. Как правило, применяются в портативных и встраиваемых системах.

Если разместить все необходимые цепи на одном полупроводниковом кристалле не удается, применяется схема из нескольких кристаллов, помещенных в единый корпус (System in a package, SiP). SoC считается более выгодной конструкцией, так как позволяет увеличить процент годных устройств при изготовлении и упростить конструкцию корпуса.

Содержание

Устройство

Типичная SoC содержит:

Блоки могут быть соединены с помощью шины собственной разработки или стандартной конструкции, например AMBA в чипах компании ARM. Если в составе чипа есть контроллер прямого доступа к памяти (ПДП), то с его помощью можно заносить данные с большой скоростью из внешних устройств напрямую в память чипа, минуя процессорное ядро.

Разработка систем-на-кристалле

Для функционирования системы программное обеспечение не менее важно, чем аппаратное. Разработка, как правило, ведётся параллельно. Аппаратная часть собирается из стандартных отлаженных блоков, для сборки программной части используются готовые подпрограммы настройки соответствующих блоков, реализующие необходимые процедуры и функции, которые в англо-язычной литературе часто называются драйверами. Применяются средства автоматизации разработки CAD и интегрированные программные оболочки.

Для того, чтобы удостовериться в правильной работе созданной комбинации блоков, драйверы и программу загружают в эмулятор аппаратной части (микросхему с программируемыми цепями, FPGA). Также требуется задать расположение блоков и разработать межблочные связи.

Перед сдачей в производство аппаратная часть тестируется на корректность с использованием языков Verilog и VHDL, а для более сложных схем — SystemVerilog, SystemC, e и OpenVera. До 70 % общих усилий на разработку затрачивается именно на этом этапе.

Системы-на-кристалле потребляют меньше энергии, стоят дешевле и работают надёжнее, чем наборы микросхем с той же функциональностью. Меньшее количество корпусов упрощает монтаж. Тем не менее, создание одной большой и сложной системы на кристалле оказывается более дорогим процессом, чем серии из маленьких, из-за сложности разработки и отладки и снижения процента выхода годных изделий.

Национальная библиотека им. Н. Э. Баумана

Bauman National Library

Персональные инструменты

SoC (System-on-a-Chip)

Систе́ма на криста́лле (СнК), однокриста́льная систе́ма (англ. System-on-a-Chip, SoC (произносится как «эс-оу-си»)) — в микроэлектронике — электронная схема, выполняющая функции целого устройства (например, компьютера) и размещенная на одной интегральной схеме.

Содержание

История

В 1976 году в Intel создали первую систему на кристалле. Это были «всего лишь» электронные часы Microma LCD watch (ссылка с фотографиями). Начинкой была система на кристалле под названием Intel 5810 CMOS chip. Прогресс на часах не остановился, Со временем, прогрессирующие технологии позволили уменьшить микросхемы и изготовить транзисторы, изготовленные по 1.5-1 микрометровой технологии (если положить в ряд 200, то они как раз займут миллиметр на линейке). По этой технологи в Intel в 1985 году сделали процессор третьего поколения 80386. Примечательна также и модель 386SL 1990 года, объединяющая на одном кристалле процессор, контроллер шины, контроллер оперативной и внешней кеш-памяти. А в 1995 появился 386EX, в кристалл которого поместили ещё контроллер прерываний, таймеры, счётчики и логику тестирования JTAG, которая используется и по сей день для прошивки и контроля качества микросхем. Несмотря на свои незначительные, по сегодняшним меркам, 25Мгц, процессор 386EX встраивали в спутники.

В 2007 году Intel анонсировала своё следущее SoC решение Intel EP80579 с кодовым названием Tolapai. На одном кристалле объединили процессор с частотой от 600 Мгц до 1200 Мгц, контроллер памяти и I/O контроллеры, а в некоторых вариациях на чипе был расположен QuickAssist для аппаратного шифрования, и его использовали, например, в vpn-решениях.

Структура

Если разместить все необходимые цепи на одном полупроводниковом кристалле не удается, применяется схема из нескольких кристаллов, помещенных в единый корпус (англ. System in a package, SiP). SoC считается более выгодной конструкцией, так как позволяет увеличить процент годных устройств при изготовлении и упростить конструкцию корпуса.

Типичная SoC содержит:

В программируемые SOC часто входят также блоки программируемых логических матриц — ПЛМ; а в прогреннаммируемые аналого-цифровые SOC — еще и программируемые аналоговые блоки. Блоки могут быть соединены с помощью шины собственной разработки или стандартной конструкции, например, AMBA[1] в чипах компании ARM. Если в составе чипа есть контроллер прямого доступа к памяти (ПДП), то с его помощью можно заносить данные с большой скоростью из внешних устройств напрямую в память чипа, минуя процессорное ядро.

Особенности проектирования СнК

В большинстве случаев СнК представляет собой цифровую СБИС, которая может также содержать ряд аналоговых блоков. Поэтому для проектирования СнК используются те же методы и средства, что и для СБИС. Эти средства реализованы в виде систем автоматизированного проектирования (САПР), поставляемых компаниями Cadance, Synopsis, Mentor Graphics и др. В качестве элементной базы эти САПР используют библиотеки функциональных элементов, в состав которых входят как простые логические вентили и триггеры, так и макроэлементы, выполняющие более сложные функции: регистры, счетчики, сумматоры, умножители, арифметико-логические устройства и т.д.

При разработке микроконтроллеров в 90-х гг. прошлого века широкое распространение получила концепция создания микроконтроллерных семейств, имеющих одинаковое процессорное ядро и различающихся набором периферийных устройств и объемом внутренней памяти. Для реализации этой концепции при проектировании СБИС микроконтроллеров кроме функциональных библиотек стали использоваться сложно-функциональные блоки (СФ-блоки) — процессоры, таймеры, АЦП, различные интерфейсные блоки (UART, SPI, CAN, Ethernet и т.д). Эти СФ-блоки формировали верхний уровень функциональных библиотек, используемых разработчиками и производителями микроконтроллеров. Они были достаточно жестко ориентированы на конкретную технологию компании-производителя, являясь внутрифирменной материальной ценностью.

Проблемы при повышении сложности

Повышение сложности проектируемых СБИС, жесткие требования к срокам их проектирования (сокращение времени выхода изделия на рынок) поставили перед разработчиками новые проблемы. В сложившихся условиях самостоятельное проектирование разработчиком СнК всех СФ-блоков, входящих в ее состав, не всегда целесообразно. Поэтому в последние годы широкое распространение получила практика разработки отдельных СФ-блоков для их последующего представления на рынок средств проектирования СнК. СФ-блоки, предназначенные для использования в разнообразных проектах, стали называть IP (Intellectual Property) модулями, тем самым подчеркивается, что эта продукция является предметом интеллектуальной собственности. СФ-блоки, используемые при проектировании СнК, имеют две основные формы представления:

Таким образом, разработчик может либо непосредственно «вмонтировать» в структуру проектируемой СБИС топологически готовый СФ-блок, либо использовать имеющуюся модель СФ-блока и выполнить его схемотехническое и топологическое проектирование в составе реализуемой СБИС СнК.

Различные решения для разработки

В процессе проектирования СнК разработчик имеет возможность выбора следующих решений:

Каждый из этих вариантов имеет свои достоинства и недостатки. Как уже отмечалось, самостоятельная разработка всех СФ-блоков может привести к увеличению сроков проектирования и задержке выпуска конечного изделия. Покупка СФ-блоков сопряжена с определенными финансовыми затратами, повышающими стоимость разработки. Применение СФ-блоков, имеющихся в свободном доступе, возможно только после их тщательной верификации, что требует обычно значительных временных затрат. При выполнении каждого проекта разработчик должен провести оценку поставленных требований и имеющихся ресурсов, чтобы выбрать оптимальный вариант реализации СнК. Таким образом, основная особенность проектирования СнК — возможность использования достаточно широкой номенклатуры синтезируемых СФ-блоков, имеющихся на рынке и в свободном доступе, которые могут быть реализованы на базе различных функциональных библиотек и технологий и интегрированы в кристалл средствами современных САПР.

Возможности реализации систем на кристалле

Технологии реализации

СнК могут быть созданы с помощью нескольких технологий, включая так называемые

Проблемы связанные с первыми технологиями

Изготовление опытной партии специализированных СБИС (несколько тысяч образцов) по технологии 0,13 — 0,18 мкм стоит несколько сотен тысяч долларов, а по технологии 0,09 мкм — свыше миллиона долларов. При этом имеющийся опыт разработки СнК показывает, что только в 25% проектов первоначально полученные опытные образцы соответствуют заданным требованиям. В большинстве случаев для получения необходимого результата требуется несколько итераций, что значительно увеличивает стоимость проекта. Можно надеяться, что развитие средств САПР позволит снизить риски при выполнении таких проектов.

Преимущества реализации СнК на базе FPGA

Преимущества реализации СнК на базе FPGA:

Таким образом, СнК на базе FPGA имеют практически те же достоинства, что и системы на плате, но отличаются лучшими техническими характеристиками — более низким энергопотреблением, меньшими габаритами и массой. При этом по таким параметрам как производительность и энергопотребление СнК на базе FPGA уступают СнК, реализованным в виде ASIC. Исходя из сказанного, можно сделать вывод, что СнК на базе FPGA будут конкурировать и постепенно вытеснять системы на плате. При этом вместо микропроцессоров и микроконтроллеров в этих СнК будут использоваться различные варианты процессорных СФ-блоков. СнК схемы обычно потребляют меньше энергии, имеют меньшую стоимость и большую надежность, чем много кристальные системы, которые они заменяют. С меньшим количеством кристаллов, стоимости сборки также снижаются. Однако у многих схем, общая стоимость больше у одного большого кристалла с той же функциональностью, нежели у нескольких маленьких схем.

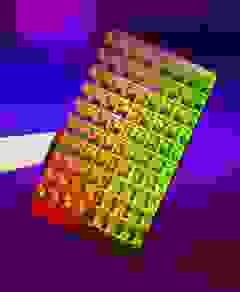

Сеть на кристалле — мини-интернет внутри процессора

У такого застоя есть объективная причина. Если разница между 2, 4 или 8 ядрами скорее количественная, то уже 16-ядерный процессор сталкивается с принципиальными ограничениями традиционной архитектуры. Дело в том, что на протяжении последних нескольких десятилетий основой коммуникации между отдельными IP-блоками чипа служила шина. Пока блоков было немного, она справлялась, но когда начали плодиться ядра, эта архитектура исчерпала себя. Шина представляет собой общую среду передачи данных, к которой подключено несколько блоков процессора. В каждый момент времени один блок может передавать данные, а все остальные — получать. Если нескольким блокам нужно передавать одновременно — возникает коллизия, а значит и задержка. При числе ядер больше восьми задержки становятся неприемлемо большими, практически полностью перечёркивая преимущества параллельной работы нескольких ядер.

Число ядер можно увеличить ещё немного, разделив шину на несколько сегментов, объединённых мостами, однако это скорее «костыль», который плохо масштабируется и не решает основную проблему. Настоящее решение, которое позволит объединять сотни блоков на одном чипе — это хорошо известная всем сеть с коммутацией пакетов, или Network on Chip.

В архитектуре NoC каждое ядро или блок процессора соединён с маршрутизатором, через который происходит его общение с другими блоками. Сами маршрутизаторы объединены в сеть, по которой пакеты данных путешествуют от одного блока к другому, так же как пакеты в обычной компьютерной сети. Это значительно упрощает топологию микросхемы и снимает ограничения по масштабированию — в отличие от шины, множество блоков способно общаться одновременно, не мешая друг другу. Компьютерное моделирование и опытные образцы многоядерных процессоров показывают, что при большом количестве ядер такая архитектура превосходит традиционную по многим показателям.

Естественно, напрямую перенести логику и протоколы работы интернета внутрь чипа было бы неразумно и неэффективно. Здесь совсем другие технологические ограничения и задачи:

Исследованиями NoC занимаются ведущие компании и университеты мира. Так, в 2007 году Intel разработала экспериментальный процессор c 80-ю ядрами и производительностью 1 терафлопс при энергопотреблении всего в 62 ватта. В 2010 был представлен 48-ядерный «Облачный компьютер на кристалле» (Single chip cloud computer).

В апреле этого года была опубликована работа группы ученых MIT, которые создали прототип 16-ядерного процессора, в котором были применены специфические для NoC-систем оптимизации — виртуальный обход (virtual bypassing) и сигналы с малой амплитудой (low-swing signaling). Эти технологии позволили приблизиться к теоретическим пределам пропускной способности и задержек и заметно снизить энергопотребление.

Как они работают? Обычный маршрутизатор сохраняет полученный пакет в буфер, анализирует его заголовок и решает, куда его отправить дальше. Virtual bypassing позволяет передать пакет практически без задержек, за счёт того, что заголовок посылается заранее, и коммутатор успевает сделать нужные переключения цепей к тому моменту, как придёт тело пакета. Таким образом, пакет идёт без остановок, минуя буфер. Low-swing signaling — это уменьшение разницы между напряжениями 0 и 1 в проводнике, за счёт чего удалось дополнительно сократить энергопотребление. В сумме эти усовершенствования поднимают пропускную способность и экономичность более чем в полтора раза.

Кроме улучшения таких характеристик, как энергопотребление и скорость, архитектура NoC даёт ещё одно важное преимущество. Она легко позволяет объединять не только однородные ядра, но и вообще любые блоки на одном чипе. Как и в компьютерных сетях, физический и транспортный уровни работают одинаково для любых типов данных и протоколов. Можно без особых проблем поставить на место одного или нескольких из универсальных вычислительных ядер любой другой IP-блок, например, графическое ядро, специализированный сигнальный процессор или контроллер какого-либо устройства. И, так же как и в сетях, можно реализовать поддержку Quality of Service на уровне чипа, что может быть полезно для систем реального времени и виртуализации.

NoC для объединения ядер процессоров пока ещё имеют экспериментальный статус, однако для объединения разнородных блоков в системах на кристалле NoC разрабатываются и применяются довольно давно. Решения таких компаний, как Sonics или Arteris используются в микросхемах Samsung, Qualcomm и даже Intel. Возможно, уже скоро сетевая архитектура начнёт вытеснять шины и из “святая святых” микроэлектроники — многоядерных центральных процессоров. И тогда число ядер снова начнёт стремительно расти. Так что закон Мура хоронить ещё рано.

Что такое SoC в оборудовании, характеристиках и для чего он нужен?

Термин SOC может относиться к Безопасность Операционный центр, но когда мы говорим о SoC (обратите внимание на строчную букву o) в аппаратном обеспечении, мы имеем в виду термин » Система на чипе «. В этой статье мы собираемся объяснить, что такое SoC, какие характеристики определяют его и какие существуют типы SoC.

По мере развития технологий, когда все стремится миниатюризировать оборудование для повышения его эффективности, мы вынуждены придумывать новую терминологию, и тем более, когда говорим о технологиях. По этой причине такой термин, как SoC, использовался в отрасли в течение нескольких лет, и хотя многие люди используют его даже ежедневно, мало кто действительно знает, что это значит.

Что такое SoC (система на чипе)?

Мы все знаем, что такое чип, но теперь вопрос в том, что считать системой? На первый взгляд, SoC выглядит как обычная микросхема, но то, что отличает SoC от обычной и обычной микросхемы, будет найдено под капотом, где сходятся большое количество различных компонентов, которые и составляют его имя, каждый из которых имеет функция, но с комбинированной функциональностью.

Другими словами, мы могли бы определить SoC как «чип, состоящий из нескольких компонентов, которые вместе составляют целостную систему».

Особенности и функции SoC

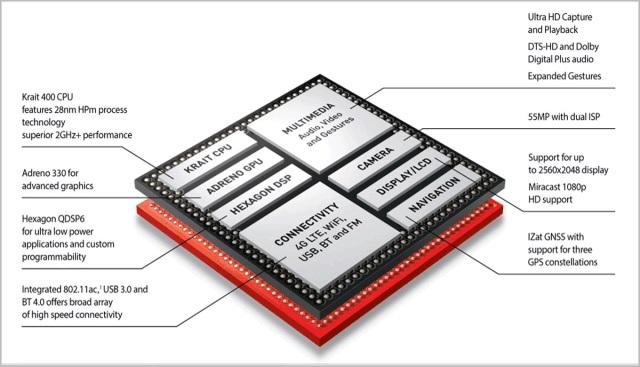

Чтобы объяснить характеристики этих элементов, мы возьмем SoC SnapDragon 801 компании Qualcomm в качестве примера, диаграмму которого вы можете увидеть ниже:

Как видно из схемы, мы находим довольно много внутренних компонентов, таких как процессор (ЦП), контроллер памяти, память, GPU / ГРАФИЧЕСКИЙ ПРОЦЕССОР, DSP, модуль подключения, обслуживающий такие технологии, как USB, LTE, Wi-Fi или Bluetooth, модуль GPS, модуль экрана, модуль камеры и, наконец, мультимедиа. Все это, что вы видите на диаграмме, на самом деле превращается в фишку размером не больше монеты.

Преимущества и недостатки

Каждая новая технология разработана для улучшения того, что уже существует, но бывают случаи, когда новый тип продукта решает существующие проблемы, но порождает новые. Таким образом, эти небольшие системы на чипе значительно улучшили то, что существовало в то время, но затем породили следующие проблемы:

В качестве преимуществ, очевидно, мы имеем миниатюризацию элемента, поскольку его небольшой размер позволяет использовать его, в частности, на мобильных устройствах. Аналогичным образом, его следующее преимущество также имеет место для мобильных устройств, поскольку это эффективность, которая способствует снижению расхода заряда аккумулятора и, следовательно, увеличению автономности.

System on chip что это

Термин «система на кристалле» (System on Chip – SoC) появился несколько лет назад, когда уровень развития полупроводниковой технологии позволил реализовывать на кристалле не только отдельные устройства, но и функционально законченные системы. В целом понятие «система на кристалле» предполагает любую более или менее сложную и функционально завершенную систему, содержащую, как правило, микропроцессорное ядро и реализуемую на отдельном кристалле. Основной способ реализации наиболее сложных систем – заказные интегральные схемы (ASIC). Для небольших проектов и в качестве вспомогательного средства используются ПЛИС. Сегодня между этими двумя полюсами – ASIC и ПЛИС – активно возникают новые способы реализации. Возможно, именно с использованием этих новых направлений будет связан следующий виток развития SoC.

СПОСОБЫ РЕАЛИЗАЦИИ СИСТЕМ НА КРИСТАЛЛЕ

В полной мере использовать возможности современных полупроводниковых технологий для достижения максимальной производительности, уменьшения потребляемой мощности и площади кристалла позволяет проектирование ASIC на основе библиотек стандартных элементов. Стоимость разработки при этом чрезвычайно высока в силу использования сложных дорогостоящих средств проектирования и необходимости создания большого числа масок (более двадцати). Кроме того, из-за сложности проектов высок риск ошибок, приводящих к необходимости перепроектирования и повторного изготовления комплекта масок.

На рис.1 приведены графики изменения стоимости изготовления полного комплекта масок для различных технологий. Видно, что после внедрения новой технологии стоимость производства со временем постепенно снижается, но в целом по новейшим технологиям ее величина растет экспонентциально. Использование новейших технологий оказывается экономически оправданным только при проектировании изделий массового применения, таких как процессоры, память, программируемая логика. Неудивительно, что число проектов ASIC в мире сокращается быстрыми темпами: с 10000 в 1998 году до 4500 в 2002 (из которых в массовое производство пошли только 3500 проектов). По некоторым оценкам, в 2003 году было начато менее 4000 проектов ASIC.

Проектирование на основе ПЛИС не связано с затратами на запуск производства, поскольку предполагает использование стандартных интегральных схем. Относительно короткий цикл и низкая стоимость средств проектирования, возможность устранения ошибок путем перепрограммирования делают реализацию проектов на основе ПЛИС весьма привлекательной. Однако большая потребляемая мощность, низкая производительность и очень высокая стоимость кристаллов по сравнению с ASIC существенно ограничивают область применения ПЛИС.

Компромиссным подходом в течение достаточно долгого времени было использование вентильных матриц, проектирование на которых, аналогично ASIC, ведется на основе библиотечных элементов, но в рамках единого, заранее разработанного и изготовленного конструктива. Базовые пластины для вентильных матриц изготавливаются массовым способом, а для создания новой интегральной схемы достаточно спроектировать и изготовить только заказные слои металла. Однако с ростом числа слоев металла при переходе на новые технологии количество заказных масок стало сравнимым с их количеством, требуемым для ASIC. При том, что в вентильных матрицах используется аналогичный ASIC продолжительный маршрут и дорогостоящие средства проектирования, а в самой концепции заложена избыточность площади кристалла, преимущества метода были сведены на нет и вентильные матрицы практически вышли из употребления.

Ниша, которую занимали вентильные матрицы, сейчас активно заполняется новыми гибридными технологиями под общим названием «структурные ASIC» (Structured ASIC). Структурные ASIC состоят из заранее спроектированной и изготовленной матрицы макроячеек (рис.2), имеющих однородную структуру (в этом смысле они похожи на ПЛИС). Как правило, все компоненты, схемы синхронизации, тестирования и самодиагностики уже реализованы, и это существенно упрощает разработку. Требуется спроектировать только от одного до трех слоев металла для функциональной настройки макроячеек и реализации межсоединений между макроячейками. Стоимость запуска в производство при этом составляет порядка 10–20% от аналогичной величины для ASIC. Даже с учетом высокой стоимости изготовления по новейшим технологиям (см. рис.1) такие затраты вполне приемлемы для разработки SoC широкой номенклатуры. При разработке структурных ASIC заранее учитываются субмикронные эффекты (электромиграция, падение напряжения на линиях связей), взаимное влияние сигналов, реализация средств синхронизации и тестирования. Поэтому маршрут проектирования существенно упрощен по сравнению с традиционными ASIC и может включать только 2–3 системы для моделирования, синтеза и планирования площади кристалла с последующим проектированием топологии на фирме-изготовителе. Время проектирования топологии также значительно сокращается (три-четыре недели от передачи списка цепей на проектирование топологии до получения готовых прототипов). Направление структурных ASIC, возникнув около двух лет назад как переосмысление концепции вентильных матриц на новом этапе эволюции полупроводниковых технологий, активно развивается. Около двух десятков компаний, таких как LSI Logic, NEC, Fujitsu, AMI Semiconductor, Lightspeed Semiconductor, Chip Express, eASIC, предлагают свои решения в этой области.

Можно привести следующие сравнительные оценки методов реализации SoC (для эквивалентных технологий). Плотность компоновки ПЛИС по сравнению с ASIC – 1% ( 90% площади кристалла ПЛИС используется только для программирования межсоединений), потребляемая мощность выше в 10–15 раз, максимальная производительность – в пределах 20%. Для структурных ASIC плотность компоновки в 50 раз выше, чем в ПЛИС, и, сответственно, составляет 40–60% от плотности стандартных ASIC. Максимальная производительность – 70%, потребляемая мощность выше в 2–3 раза, чем для стандартных ASIC.

В целом аналитики полагают, что время широкого использования ASIC на основе библиотек стандартных элементов проходит. Конечно, за ними останется область массовых и уникальных по характеристикам изделий, но для большинства интегральных схем со средними объемами выпуска будут использоваться именно структурные ASIC, а ПЛИС прочно займут свою нишу в сфере низкопроизводительных приложений с малыми объемами выпуска. Прогнозируемый объем рынка структурных ASIC оценивается в 2–5 миллиардов долларов, которые практически целиком «изымаются» с рынка традиционных ASIC при сохранении положительной динамики роста рынка ПЛИС.

Способы реализации систем на кристалле не ограничиваются вышеперечисленными методами. Существует ряд промежуточных вариантов, которые можно определить как конфигурируемые системы на кристалле (Configurable System on Chip – CsoC). Такие комбинированные методы строятся на сочетании нескольких подходов, могут включать полностью заказные блоки, например микропроцессорные ядра, блоки на основе библиотек стандартных элементов, структурных матриц и полей программируемой логики. Практической реализацией одного из таких методов является серия микросхем компании Triscend, которые могут включать поля программируемой логики, 32-разрядное процессорное ядро ARM7TDMI, микроконтроллер 8051. Компании Lightspeed и eASIC используют подход, при котором разрабатываются структурные блоки, встраиваемые в ASIC. Кристаллы компании Leopard Logic представляют собой комбинацию большого структурного блока и нескольких полей программируемой логики.

Системы на кристалле в полной мере можно реализовать и на современных ПЛИС. Такие проекты получили название «системы на программируемом кристалле» (System on Programmable Chip – SoPC). Действительно, здесь могут присутствовать все компоненты, свойственные системам на кристалле в традиционном понимании: процессорные ядра, память, IP-блоки. Покупка Triscend компанией Xilinx в феврале этого года и разработка компанией Altera серии программируемых масками микросхем Stratix HardCopy показывают, что производители традиционных ПЛИС, со своей стороны, стремятся выйти на рынок более эффективных решений. Средства проектирования по мере усложнения ПЛИС также усложняются, маршрут проектирования начинает походить на маршрут для традиционных ASIC. Включаются этапы планировки площади кристалла, физического синтеза и формальной верификации. Действительно, когда одна итерация цикла проектирования топологии ПЛИС объемом шесть миллионов вентилей занимает сутки, а количество итераций измеряется десятками, оценка временных и прочих ограничений на ранних стадиях, еше до проектирования топологии, становится актуальной задачей. К тому же, поскольку все большая часть проектов ASIC макетируется на ПЛИС (прогноз на ближайшее время – до 80% от общего числа), а успешные ПЛИС-проекты могут переноситься на ASIC, желательно, чтобы и в маршруте, и в средствах проектирования заранее учитывалась возможность перехода на другой вариант реализации.

Итак, между ASIC и ПЛИС развивается целый спектр методов реализации систем на кристалле, происходит взаимопроникновение, комбинирование подходов с целью поиска вариантов наиболее эффективных с технической и экономической точки зрения. Структурные ASIC оказываются реальной альтернативой как ПЛИС, так и ASIC. Объемы производства, при которых их применение может быть экономически целесообразно, оцениваются от одной тысячи до ста тысяч микросхем в год.

ИСПОЛЬЗОВАНИЕ IP-БЛОКОВ

Одновременно с появлением концепции системы на кристалле возникли идеи создания методологии проектирования на основе унифицированных наборов готовых базовых блоков (платформ). Интерфейсы компонентов платформы (процессоров, блоков памяти и управления, шинных интерфейсов и др.) в рамках достаточно широкого класса задач должны быть унифицированы, чтобы новые устройства можно было «собирать» из блоков, как конструктор. Причем «собирать» на системном уровне, уровне функционального описания, проводя анализ и глобальную оптимизацию всей системы в целом, а далее использовать готовые аппаратные решения, заложенные в описаниях базовых блоков (IP-блоков). В силу проблем с созданием переносимой универсальной аппаратной начинки блоков, которую можно было бы переиспользовать при производстве по различным технологиям, на различных фабриках в целом внедрение такого подхода в качестве универсальной методологии не оправдалось. Однако это дало толчок развитию индустрии IP-блоков. В результате сейчас существует большой выбор библиотек специализированных IP-блоков для различных прикладных областей и технологий изготовления микросхем, в частности библиотек IP-блоков для ПЛИС, представленных в виде синтезируемых блоков на языках высокого уровня, списков цепей в элементном базисе производителей ПЛИС и готовых макросов с топологической реализацией.

Структурные ASIC также обычно сопровождаются библиотеками IP-блоков. Это позволяет говорить о них как о готовых платформах для реализации систем на кристалле. Например, библиотека структурных ASIC компании LSI Logic включает более четырехсот элементов. Кроме того, может использоваться библиотека IP-блоков CoreWare, содержащая процессоры, периферийные блоки, компоненты шины AMBA, интерфейсы памяти и др. Для реализации процессорных ядер (ARM, MIPS, сигнальный процессор ZSP) предусмотрены специальные области. Если такие процессоры не используются, в этих областях можно реализовывать и произвольную логику. Процессоры, как и другие IP-блоки библиотек, верифицированы и могут использоваться в виде готовых макросов.

СРЕДСТВА СИСТЕМНОГО ПРОЕКТИРОВАНИЯ

Понятие системного уровня проектирования фактически включает в себя все, что лежит выше уровня разработки RTL. Здесь создается модель исполняемой спецификации, которая служит эталоном поведения проектируемой системы на всех последующих этапах. В системном проектировании можно выделить три уровня детализации:

· уровень «миссии» и выбора общей концепции построения системы, включающий моделирование операционной среды, в которой будет работать проектируемая система, определение статических и динамических сценариев, планирование целевых задач;

· архитектурный уровень с моделированием и анализом производительности систем, сетевых архитектур и протоколов, пропускной способности каналов;

· уровень микроархитектуры, т.е. моделирование и анализ алгоритмов, протоколов, схем разрешения конфликтов на шинах, методов управления памятью, программно-аппаратное разделение и разработка программного обеспечения (драйверы и др.).

Если первые два уровня относятся к задаче концептуального построения и анализа системы, то микроархитектура непосредственно связана с последующим этапом функционального проектирования. Сегодня, когда методология проектирования на RTL-уровне в общем устоялась, именно в области средств проектирования микроархитектуры инновации наиболее активны. В первую очередь это связано с применением языка С/С++ и производных языков на его основе, таких как SystemC, Handel-C, Stream-C и других для разработки моделей аппаратных блоков. Идея использования моделей высокого уровня, реализованных на языках программирования не нова, но сейчас поддержка таких языков обеспечивается не только в системах моделирования, но и в системах синтеза.

Так, проекты созданные в одной из популярных систем разработки и моделирования алгоритмов цифровой обработки сигналов Matlab/Simulink, обычно использовались как спецификации для ручного кодирования моделей на уровне RTL. Разработанная компаний AccelChip система синтеза высокого уровня теперь позволяет сгенерировать синтезируемые RTL-модели на языках VHDL и Verilog напрямую из Matlab с поддержкой автоматического преобразования арифметики плавающей точки в фиксированную.

Другой подход используется компанией Celoxica в системе DK2 Design Suite, которая реализует методологию программного компилятивного проектирования. Среда проектирования позволяет выполнить общую модель и верификацию проекта на языке С, провести разделение на программную и аппаратную части и напрямую синтезировать последнюю в элементный базис ПЛИС или в код VHDL/Verilog. Поддерживаются языки C, C++, SystemC и Handel-C, а также компиляция исходных кодов в процессорные ядра, например Xilinx MicroBlaze. Это дает возможность, не меняя исходной спецификации алгоритма, быстро реализовать его в макетном варианте на процессорном ядре ПЛИС, провести оптимизацию с частичной или полной аппаратной реализацией и затем, при необходимости, сгенерировать код RTL для перевода на ASIC.

Обеспечение целостности исходных спецификаций при их трансформации с верхнего уровня на уровень функционального проектирования имеет принципиальное значение. Поэтому фирмы-разработчики систем логического моделирования стремятся обеспечить совместное моделирование и поддержку VHDL, Verilog, C/C++, SystemC и других языков из единой интегрированной среды проектирования. Например, помимо перечисленных языков, системы моделирования компании Aldec обеспечивают совместное моделирование с Matlab/Simulink, имеют встроенные системы отладки С/С++ и Handel-C и встроенные интерфейсы с системами AccelChip и Celoxica, так что разработчики могут в рамках единой среды проектирования выполнять разработку и отладку кода, моделирование и синтез с гибкой настройкой системы на свой маршрут проектирования.

СРЕДСТВА ФУНКЦИОНАЛЬНОГО ПРОЕКТИРОВАНИЯ

Функциональный уровень на сегодняшний день остается основным при проектировании цифровых систем независимо от их физической реализации. Задача разработчика на функциональном уровне – создать RTL-описание системы, из которого можно средствами логического синтеза получить работоспособный проект. Поэтому к средствам функционального проектирования обычно относят средства моделирования и отладки RTL-кода а также средства логического синтеза из RTL-описаний.

Процесс отладки RTL-кода носит итерационный характер. Уменьшение числа итераций – прямой путь к сокращению стоимости и сроков разработки. Решение этой задачи напрямую связано с созданием средств контроля качества исходного кода, оценки его реализуемости на ранних стадиях выполнения проектов еще до этапа логического синтеза. Кроме того, использование таких средств позволяет обеспечить переносимость проектов с ПЛИС на ASIC. Не секрет, что разработчики ПЛИС зачастую не заботятся о качестве создаваемого VHDL- или Verilog- описания. Ведь всегда можно поправить код и перепрограммировать ПЛИС. А когда работоспособный вариант получен, то до чистки и оптимизации руки, как правило, уже не доходят. В результате казалось бы уже выполненный проект при переносе на ASIC требует существенной переработки и детальной повторной верификации. Использование средств контроля качества на ранних стадиях позволяет значительно облегчить задачу переноса.

Первые поколения таких систем были ограничены лишь проверкой семантики, сейчас появились системы, которые учитывают целостность, завершенность проекта, стиль кодирования, временные ограничения, выполняют анализ площади блоков, нетрассируемых структур и времени распространения сигналов. Важно здесь то, что эти системы дают возможность разработчику оценить реализацию своего проекта на ранней стадии без необходимости иметь знания о физических аспектах дальнейших этапов проектирования. Более того, такой формальный анализ кода на уровне RTL не только повышает качество проекта и сокращает число итераций при логическом синтезе, но и в перспективе дает возможность передачи на завершающие этапы проектирования в специализированные дизайн-центры не списка цепей в элементном базисе производителя, а RTL-кода на языках VHDL или Verilog. Например, компании LSI Logic и NEC для анализа проектов с учетом возможности их реализации на своих структурных ASIC используют специально настроенный САПР компании Tera Systems. Компания IBM также использует средства Tera Systems в перспективном маршруте проектирования ASIC c приемом от заказчиков на финальное проектирование кода на уровне RTL.

Использование предварительного анализа – вещь, конечно, очень полезная, но в любом случае рабочей лошадью для отладки RTL-кода служат средства моделирования. Разработчик создает новые фрагменты кода, запускает моделирование полученной системы, после анализа результатов вносит изменения в код. И так до тех пор, пока не добьется требуемых результатов моделирования. Для ПЛИС, где в основе проектирования лежит принцип «всегда можно все исправить», потребительские характеристики систем моделирования определяются простотой, удобством отладки проектов, низкой стоимостью. Для ASIC (в том числе и структурных) нужно «сделать сразу все правильно». Поэтому основным здесь становится качество логической и временной верификации, даже за счет высокой стоимости систем моделирования.

Сегодня наиболее популярными системами моделирования являются продукты компаний Aldec, Cadence, Mentor Graphics и Synopsys. Если средства Cadence и Synopsys в основном используются в маршрутах проектирования ASIC, то системы моделирования Active-HDL, Riviera компании Aldec и ModelSim компании Mentor Graphics поддерживают также всех производителей ПЛИС. Так, САПР Active-HDL обеспечивает единую интегрированную среду проектирования и моделирования для ПЛИС любых производителей, содержит средства групповой разработки, управления проектами и библиотеками, кросс-отладки и анализа тестового покрытия, текстовые и графические редакторы, а вместе с системой Riviera, включающей в себя ряд специальных средств для верификации ASIC, предоставляет единую среду проектирования для всех возможных способов реализации проектов.

До тех пор, пока передача проекта на разработку топологии осуществляется на уровне списка цепей, разработчикам функционального уровня необходимо будет иметь у себя средства логического и физического синтеза. При всем многобразии подобных средств наиболее универсальным на сегодняшний день является продукт компании Synplicity. Средства Synplicity позволяют проводить логический и физический синтез для ASIC и ПЛИС любых производителей, поддерживают макетирование ASIC на ПЛИС с возможностью автоматического разбиения проекта (с сохранением целостности) на множество ПЛИС, имеют средства отладки прошивок ПЛИС на уровне исходного RTL-описания.

Компания Synplicity наиболее заметна и в плане поддержки синтеза для структурных ASIC. Для структурных ASIC можно использовать и традиционные средства логического синтеза ASIC. Но достижение хороших результатов при логическом синтезе возможно только при специальной настройке на элементный базис используемых структурных ASIC ( обычно более крупный, ближе к ПЛИС, включающий мультиплексоры, триггеры, память). Показательно, что именно систему физического синтеза Synplicity AmplifyASIC, адаптированную под архитектуру своих структурных ASIC, используют такие компании, как LSI Logic и NEC.

В заключение надо заметить, что хотя каждый из производителей строит свой маршрут проектирования, ориентированый на конкретную архитектуру, в целом направление структурных ASIC стимулирует развитие адаптивных коммерческих САПР и методологии функционального проектирования на основе средств формального анализа и контроля реализуемости RTL-описаний. Это может иметь широкое прикладное значение. Эффективный контроль и прогнозирование на функциональном уровне существенно сокращают число итераций и время проектирования. А создание адаптивных средств САПР для отдельных этапов проектирования (моделирование, синтез), при стандартизации переходов от этапа к этапу, позволит обеспечить более высокую степень технологической (от способа реализации) и организационной (от производителя САПР) независимости при организации разработок систем на кристалле.

КОМПАНИИ-ПРОИЗВОДИТЕЛИ СТРУКТУРНЫХ ASIC И СРЕДСТВ САПР ДЛЯ НИХ